|

RDRAM의 동작방법

1. RDRAM 프로토콜(Protocol)

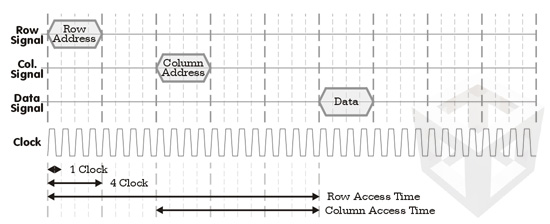

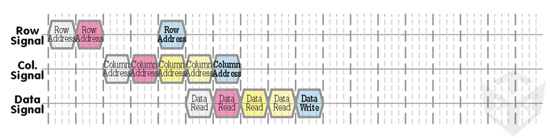

RDRAM의 프로토콜을 이해하는데에 있어서 가장 중요한

것은 RDRAM은 모든 데이터와 명령어셋을 패킷의 형태로 전달한다는 것과,

Row 명령어 및 Collumn 명령어가 별도의 신호선을 통해서 전달된다는

것이다.

이들 패킷은 모두 4클럭(PC800 RDRAM에서는 10ns(400MHz의

DDR동작이므로 한번의 클럭은 2.5ns), PC1066에서는 533MHz의 동작이므로

7.5ns)의 길이를 가진다.

Row 명령어의 패킷은 24bit로 이루어지며, 여기에는

데이터 전송이 일어날 디바이스와 열, 뱅크를 지정한다. 또한,

데이터 전송이 일어날 메모리의 활성화와 프리챠지(precharge)를 수행한다.

Col 명령어 패킷은 40bit로 구성되어 있으며, 데이터전송이 일어날 디바이스와

행, 뱅크를 지정한다. 여기에는 읽기/쓰기에 대한 실질적인 명령이 포함되어

있다.

Row 명령어가 해당 메모리로 전달되면 메모리 중에서

데이터를 읽어들일 부분, 즉 지정된 디바이스의 지정된 뱅크에 있는

지정된 열의 활성화와 프리챠지가 일어난다. 그리고, Col 명령어가 전달되면

앞서 지정된 디바이스, 뱅크에 있는 해당 행에서 데이터의 입출력 명령이

전해진다. 그러면, 데이터의 읽기/쓰기가 16byte 단위로 일어난다. 1번의

패킷이 4 클럭에 해당하므로, DDR이 적용될 경우 8번의 전송이 일어날

수 있다. 그리고 RDRAM 디바이스는 16bit의 데이터 버스를 가지고 있으므로

하나의 패킷에서 16bit×4×2=128bit=16byte가 전송되는 것이다.

이 때, 각각의 신호선은 완전히 분리되어 있다. 이것은

데이터의 전송과정중에 발생하는 여러가지 문제점을 줄여줄 수 있다.

RDRAM에서의 데이터 전송이 일어나는 과정을 살펴보면 다음과 같다.

우선, 데이터의 읽기 신호가 들어왔다고 하자. 그러면,

앞서 설명했던 대로 Row 명령어 패킷이 전해지고, 이후 Col 명령어 패킷이 전해진다.

그리고 이들 명령어를 받아서 데이터를 읽어내어 출력한다. Row 명령어가

입력된 후 출력되기까지 소모된 클럭은 총 20클럭이다. 그리고, 바로

다음에 새로운 읽기 명령이 입력된다.

새로운 명령어는 앞서의 Row 명령어가 입력된 바로

다음에 입력될 수 있다. 그리고 같은 주기로 Col 명령어의 입력과 데이터의

출력이 행해진다. 만약 Row 신호와 Col 신호가 같은 신호선을 통해서

전달된다면, 다음 명령어의 입력을 위해서는 앞서의 데이터 출력이 모두

완료되어야만 한다. 그러나 RDRAM에서는 Row 명령어와 Col 명령어를

서로 다른 신호선을 통해서 전송함으로써 그러한 지연시간을 최소화한

것이다.

또다른 읽기 요청이 들어왔다. 단, 이번의 읽기 요청의

경우 이전에 읽었던 부분과 연속되어 있는 부분의 데이터를 읽어들이기

위한 것이다. 즉, 연속되어 있는 데이터에서 이미 이전에 읽었더(open되어

있는) 페이지에 데이터가 존재할 경우나 동일한 데이터를 다시 읽어들일

경우에는 Row 신호가 생략되고 바로 Col 명령어만이 입력된다. 그리고

역시 같은 속도로 데이터의 전송은 진행된다.

이제 쓰기 명령이 입력되었을 경우를 생각해보자.

새로운 쓰기 명령에 대해서 Row 명령어가 입력되고, Col 명령어 역시

입력된다. 그리고 데이터의 기록이 일어난다. 이 과정에서, 읽기와 쓰기에

대한 지연시간이 존재하지 않는다는 것이 바로 RDRAM 프로토콜의 가장

큰 장점이다. 이렇게 연속적인 읽기/쓰기가 일어날 수 있는 것은 하나의

메모리 디바이스가 명령에 반응하고 있는 동안 다른 메모리 디바이스가

다음 명령어에 반응하기 때문이다. 이는 RDRAM의 구조가 직렬 구조이기

때문이기도 하다.

결국, RDRAM에서의 데이터 전송은 연속적인 데이터가

지연시간 없이 패킷 형태로 전송될 수 있다. 또한 읽기/쓰기 전환시의

지연시간 역시 존재하지 않는다. 이러한 특징으로 인해서 RDRAM은 대단히

높은 실효 전송 대역폭을 실현한다.

2. 동작구조

지금까지는 RDRAM의 내부적인 동작을 살펴보았다.

그러면, RDRAM이 외부적으로는 어떠한 구조를 가지고 동작하는가를 알아볼

차례이다.

다수의 뱅크와 뱅크 인터리브

RDRAM은 기본적으로 직렬 버스 하에서 동작한다.

그래서 칩의 연결구조(토폴로지 : topology)부터 다르며, 뱅크의 연결방향

또한 다르다. 그래서 기존의 SDRAM과는 상당히 여러가지 특징을 가지게

된다. 우선, 토폴로지를 이해하기 전에 뱅크부터 살펴보아야 한다. 여기서 말하는 뱅크(bank)라는

것은 '센스 앰플리파이어를 공유하는 메모리 블록의 집합'이라고 정의된다.

여기서, 센스 앰플리파이어란 DRAM의 각 셀들로부터 데이터를 읽어들이고

주기적인 리프레시를 행하고 데이터를 복구하는 역할을 하는 DRAM의

한 부분이다. 즉, 뱅크라는 것은 같은 센스 앰플리파이어에 의해서 같은

타이밍으로 데이터의 리프레시가 행해지는 영역을 의미한다.

RDRAM은 앞서도 언급했다시피 Row 명령어와 Col 명령어,

그리고 데이터의 전송에 각기 별도의 버스를 사용한다. 이들 버스는

모두 16bit(또는 18bit)로 구성되어 있다. 그래서 다음과 같은 형태가

된다.

RDRAM 칩 하나는 내부적으로 32개의 뱅크를 갖는다.

그런데, 32개의 뱅크를 갖는다는 것은 32개의 센스 앰플리파이어를 갖는다는

말과 갖다. 보다 많은 뱅크를 가진다는 것은 성능의 향상으로 이어질

수 있다. 이것은 뱅크 인터리브(bank interleave)라는 기술 때문이다.

|

|

뱅크 인터리브(Bank Interleave) |

|

바이오스 등에서 뱅크 인터리브라는 것을 봤지만 정작 이것이

무엇을 의미하는지 애매한 사용자가 많을 것이다. 특히,

메모리는 모두 6개 혹은 8개의 뱅크를 가지는데 왜 뱅크

인터리브는 4개까지밖에 되지 않는가 하는 질문을 가지는

사용자도 있다. 그러나 흔히 말하는 메모리 뱅크와 뱅크

인터리브에서 말하는 뱅크의 개념은 서로 다르다. 뱅크

인터리브에서 의미하는 메모리 뱅크는 바로 위에 설명한

대로이다. 대개의 SDRAM의 경우 메모리 자체가 4개의 뱅크를

가지고 있다.

뱅크 인터리브는 CPU의 데이터 처리

파이프라인처럼 뱅크를 사용한다고 이해하면 쉽다. 만약

메모리가 하나의 뱅크만을 가지고 있을 경우 이 메모리는

다음과 같이 데이터입출력을 행하게 된다.

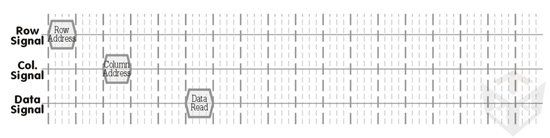

여기서 붉은색은

Row Command, 파란색은

Column Command, 녹색은

Data 전송을 의미한다.

위의 일러스트는 단일 뱅크에서 데이터의

입출력이 어떻게 일어나는가를 보여준다. Row 명령어, Col

명령어, Data 전달이 순차적으로 반복된다. 앞서 입력된

데이터 입출력요구가 끝나기 전까지 다음의 데이터는 대기해야만

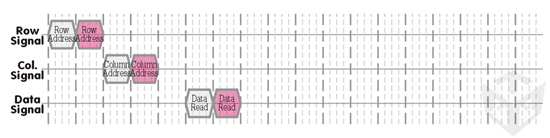

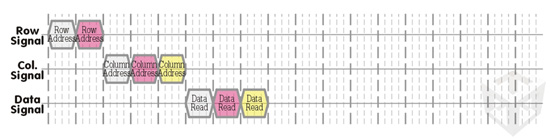

한다. 그러나 뱅크가 많을 경우는 어떻게 될까. 4개의 뱅크를

사용해서 뱅크 인터리브를 할 경우를 가정하면 다음과 같다.

하나의 칩 안에는 4개의 뱅크가 들어있다.

그리고 Row 명령어가 들어온 다음에 해당 뱅크가 Col 명령어를

받는 동안 다음 뱅크에는 Row 명령어가 입력되고 있다.

그리고, 첫번째로 명령을 받은 뱅크가 데이터 입출력을

행하는 동안 두번째 뱅크는 Col 명령어를 받고 있으며,

세번째 뱅크에서는 또 Row 명령어를 받아들이고 있다. 이러한

방식을 사용해서 4개의 뱅크를 사용한 인터리브 기법을

사용하면 이론적으로 400%의 성능향상이 이루어진다고 생각할

수 있다.

물론 이것은 이론적인 것이다. 현실적으로는

여러가지 문제가 발생한다. 우선, 위의 일러스트는

Row 명령어, Col 명령어 등이 모두 동시에 들어올 수 있다는

것을 가정한, 즉 RDRAM을 가정한 경우이다. SDRAM의 경우

Row, Col 명령어가 동시에 입력될 수 없기 때문에 위의

상황과는 좀 다르다.

그리고 뱅크 충돌(bank conflict)라는

것이 있다. 뱅크 충돌은 현재 데이터의 읽기/쓰기 작업이

행해지고 있는 뱅크에 있는 데이터를 시스템이 요구할 때

발생한다. 만약 메모리가 4개의 뱅크를 가지고 있고, 현재

작업하는 명령 외에 추가적인 1개의 작업을 더 할당받는다면

25%(1/4)의 뱅크 충돌 확률이 존재한다. 만약 2개의 작업이

더 할당된다면 50%(2/4)의 뱅크 충돌 확률이 만들어진다.

대개 메모리의 데이터 입출력 내용 중 25%는 바로 이전에

데이터 입출력이 일어났던 부분에 대한 입출력 요구이기

때문에 이러한 뱅크 충돌로 인해서 이론적인 성능향상폭을

모두 기대할 수는 없다.

|

만약, 32개의 뱅크를 가진다면 뱅크 충돌의 확률이 현저히 떨어진다.

메모리에 현재 작업중인 명령 외에 1개의 입출력요구가 더 발생했다면

3.125%(1/32)의 뱅크 충돌 확률이 있으며, 2개의 입출력요구가 있다고

해도 6.25%(2/32)라는 적은 확률로 뱅크 충돌이 일어난다. 그래서 보다

많은 뱅크는 성능의 향상을 이룰 수 있다.

그런데, 뱅크의 수가 많아지는 것이 꼭 장점만이

되지는 못한다. 앞서 언급한 내용에서 유추할 수 있듯이, 뱅크가 많아진다는

것은 곧 센스 앰플리파이어의 수가 그에 비례해서 증가한다는 것을 의미한다.

센스 앰플리파이어는 메모리 칩 내에서 적지않은 면적을 차지하며, 그

결과 많은 뱅크를 가지는 메모리는 그 가격이 상당히 비싸진다. 초기에

만들어지는 128/256Mbit RDRAM은 하나의 칩이 32개의 뱅크를 가지고

있었다. (물론 다른 이유도 충분히 많았겠지만) 그래서 메모리의 가격이

상당히 비쌌다. 그러나 후기에 생산된 128/256Mbit 메모리와 512Mbit

메모리들은 4개의 뱅크를 가지는 구성(4i라고 하며, 이는 4 independant

bank core를 의미한다)으로 되어 있어서 초기의 RDRAM보다 저렴하다.

여기서, 뱅크의 숫자가 줄어든다고 해서 성능이 줄어들것이라고

생각할 수 있지만, 뱅크수의 감소로 인한 성능감소는 의외로 거의 일어나지

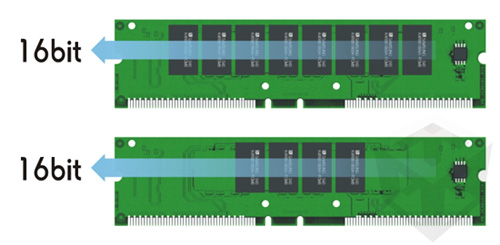

않는다. RDRAM의 직렬구조 때문이다. RDRAM은 모든 칩이 직렬로 연결되며,

칩의 숫자가 데이터 버스의 폭에 영향을 주지 못한다.

칩이 몇개가 연결되던 버스폭에는 변동을 주지 않기

때문에, 기기 자체의 제약(RDRAM은 최대 32개까지의 칩(device)을 직렬로

연결할 수 있다.)을 넘어가지 않는 한 몇개를 붙여도 상관없다. 또한,

뱅크의 나열방향이 칩의 연결방향과 같다. 그래서 4개의 뱅크를 가지는

칩이라면 8개의 칩을 모듈에 장착해서 32개의 뱅크를 구성할 수가 있는

것이다. 결국, 칩의 수를 늘리면 되기 때문에 하나의 칩에서 뱅크가

줄었다고 해서 큰 성능하락이 발생하지는 않는다.

모듈의 구성과 최대 모듈의 수

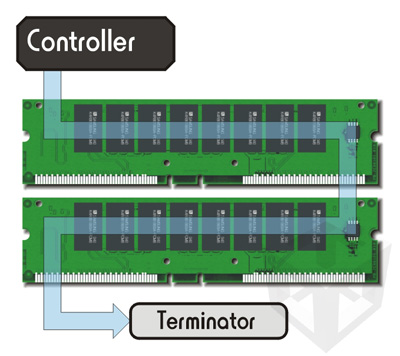

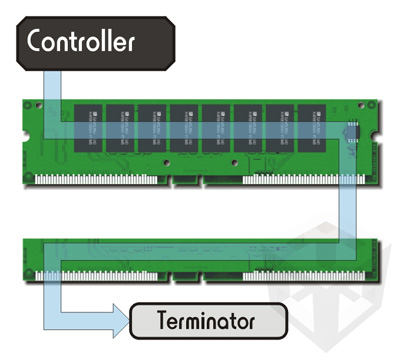

RDRAM 내부의 칩들이 직렬로 연결되는 것과 마찬가지로,

RDRAM의 모듈 역시 모두 직렬로 연결된다. 2개의 RDRAM 모듈이 장착되는

경우의 연결도는 다음과 같다.

여기서 터미네이터(Terminator)는 신호를 끝내주는

부분이다. 램버스 메모리는 전체가 직렬로 연결되어 있기 때문에 신호가

끝나는 부분을 정해주어야만 한다. 터미네이터는 신호가 끝나는 부분임과

동시에, 신호선을 타고 나온 각 신호들이 끝단에서 반사되어서 케이블

중간에서 간섭을 일으키지 않도록 하는 역할을 한다. 컨트롤러에서 나온

신호는 모든 RIMM 모듈을 거쳐서 터미네이터까지 이어지는 하나의

직렬 회로를 구성하게 된다.

RDRAM에서는 하나의 채널에서 최대 2개의 모듈을

사용할 수 있다. 이것은 몇가지 요인에 의해서 제한받고 있기 때문이다.

우선 칩의 숫자에 의한 제약을 받는다. RDRAM의 직렬

회로는 총 32개의 디바이스가 연결될 수 있다. 즉, 32개의 칩이 연결될

수 있다는 것이다. RIMM(RDRAM Dual Inline Memory Module)은 최소 2개에서

최대 16개까지의 칩을 사용한다.(SDRAM과는 달리 몇개의 칩을 사용하는가에

관계없이 동일한 칩을 사용할 수 있다. 이것에 대해서는 뒤페이지에서

다시 언급한다) 만약 2/4/8개의 칩을 사용하는 RIMM이라면 이야기가

달라지겠지만, 만약 16개의 칩을 탑재한 RIMM을 사용한다면 2개의 RIMM

만으로도 32개의 디바이스가 모두 차버린다.

두번째, 타이밍의 문제이다. 가장 처음 출시되었던

RDRAM 지원칩셋인 i820 칩셋의 경우 초기에 3개까지의 RDRAM 모듈을

지원하였다. 그러나 이들이 모두 직렬로 연결되는 까닭에 3개의 모듈을

사용하면 전체 회로의 길이가 지나치게 길어진다. 아무리 전선이 신호를

빨리 전달한다고는 하나 RDRAM 자체가 워낙 높은 클럭으로 동작하기

때문에 이러한 회로의 길이 연장은 신호의 안정성에 상당한 악영향을

초래한다. 그래서 인텔에서는 안정성 및 데이터의 신뢰도를 향상시키기

위해서 하나의 채널에 사용할 수 있는 RIMM의 개수를 2개로 제한하였다.

|

|

4개 혹은 8개의 RDRAM을 사용하는 메인보드는?? |

|

RDRAM은 하나의 채널에서 2개의 모듈만을 사용할 수 있다고 언급하였다.

그런데, i850 칩셋 메인보드는 당장 4개의 RDRAM 모듈을

지원할 수 있으며, i860 칩셋 기반의 메인보드 중 일부는

8개까지의 RDRAM을 사용하기도 한다. 이들은 어떻게 해서

최대 8개까지의 RDRAM을 사용하는것일까?

1. i850 칩셋

지극히 간단하다. 850 칩셋은 듀얼채널이다.

분명히 필자는 '하나의 채널에서 2개의 모듈을 사용할 수

있다'라고 했다. 즉, 2개의 채널을 사용하기 때문에 총

4개까지의 메모리를 지원하는 것이다. 물론, 이러한 경우에

듀얼 채널을 구성해서 사용해야 하기 때문에 최소한 양쪽

채널에 하나씩의 메모리는 있어야한다. 최소한 2개의 동일한

메모리 모듈이 필요하다는 것이다.

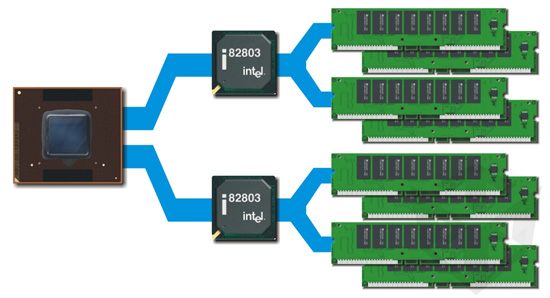

2. i860 칩셋에서의 8개의 RDRAM

사용

사실,

i860 칩셋 역시 RDRAM의 지원에 있어서는 i850 칩셋과 동일하다.

단지 CPU의 지원만 틀릴 뿐이다. 그러면 어떻게 해서 8개까지의

RDRAM을 사용할 수 있는 것일까. 여기에는 인텔의 i82803

MRH(Memory Repeater Hub)가 관련되어 있다. 사실,

i860 칩셋 역시 RDRAM의 지원에 있어서는 i850 칩셋과 동일하다.

단지 CPU의 지원만 틀릴 뿐이다. 그러면 어떻게 해서 8개까지의

RDRAM을 사용할 수 있는 것일까. 여기에는 인텔의 i82803

MRH(Memory Repeater Hub)가 관련되어 있다.

MRH는 하나의 메모리 채널을 받아서

이를 두개로 분할해 준다. 그렇다고 해서 이것이 두개의

메모리 채널이 되는 것은 아니며, 메모리 대역폭은 동일하게

유지하면서 사용할 수 있는 최대 모듈의 숫자만 2배로 늘려주는

것이다. 그래서 MRH를 사용하면 16개까지의 RDRAM도 사용할

수 있지만, 공간적인 문제로 인해서 그러한 메인보드는

좀체로 찾아보기 어렵다.

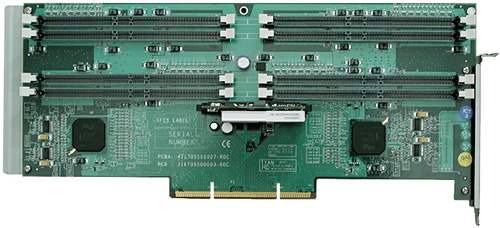

이러한 구성이 실제로 적용된 예는 바로

Tyan의 Thunder

i860(S2603) 메인보드이다. 이 메인보드는 보드상에는

메모리 슬롯이 없고, 단지 MEC(Memory Expansion Card)의

슬롯만이 있을 뿐이다.(이 슬롯은 펜티엄 II/III Xeon에

사용되었던 Slot 2와 동일하다. Slot2는 핀이 3중으로 되어

있어서 핀 수도 많고 데이터신뢰도에 대한 고려도 보다

잘 되어 있는 것이 사실이긴 하지만 원가절감을 위해서

그냥 가지고 있던 자재(예전에 펜II/III Xeon용 보드를

만들다가 남은.. -_-)를 사용하기 위해서가 아닐까 하는 생각이

부쩍 든다.)

M2603

MEC (Tyan

홈페이지에서 발췌)

메모리를 총 8개 사용할 수 있는 것처럼

보이는데, 아래쪽에 보이는 2개의 칩셋이 바로 i82803 MRH이다.

이를 사용하여 2개의 채널에서 각 채널당 4개의 RIMM을

사용하도록 한 것이다. 이 메인보드 역시 한번에 2개씩의

메모리를 사용해야 하며, 비어있는 곳에는 모두 RDRAM 연속성

모듈을 장착해 주어야 한다.

|

RDRAM 연속성 모듈

만약 1개의 모듈만을 사용해야 하는 경우라면 어떻게

될까? 이러한 경우에 컨트롤러부터 터미네이터까지 이어지는 전체 신호선이

끊기고 만다. 그래서 이렇게 끊어진 회로를 이어주기 위해서 별도의

모듈을 장착하게 되는데, 그것이 바로 RDRAM 연속성 모듈(RDRAM Continuity

Module)이다.

RDRAM 연속성 모듈의 추가로 회로는 완성되고 전체적인

직렬 회로가 구성되는 것이다. 이것은 단지 회로를 이어주는 역할만을

하기 때문에 아무런 컴포넌트가 붙어있지 않다. 단지 해당 핀을 연결해주는

것에 불과하다. 그러나 연속성모듈이 없으면 RDRAM의 RaSer의 회로는

구성되지 않으며, 시스템은 동작하지 않는다.

이것을 터미네이터로 잘못 알고 있는 사용자들이

대단히 많다. 그러나 터미네이터는 메인보드상에 내장되어 있으며, 연속성

모듈 자체에는 터미네이션 기능이 포함되어 있지 않다.

|